# **TECHNICAL TRANSACTIONS**

# CZASOPISMO TECHNICZNE

**ELECTRICAL ENGINEERING**

**ELEKTROTECHNIKA**

2-E/2016

DOI: 10.4467/2353737XCT.16.243.6042

WITOLD MAZGAJ, BARTOSZ ROZEGNAŁ, ZBIGNIEW SZULAR\*

# A NOVEL SOFT SWITCHING SYSTEM FOR THREE-PHASE VOLTAGE SOURCE INVERTER

# TRÓJFAZOWY FALOWNIK NAPIĘCIA Z NOWYM UKŁADEM ŁAGODNEGO PRZEŁĄCZANIA

#### Abstract

Soft switching systems in three-phase voltage source inverters usually require the use of additional elements, such as transistors, capacitors and inductors. Contrary to the existing solutions, in the proposed soft switching system, the danger of an abrupt discharge of the capacitors through the conductive transistor does not occur. Moreover, there is no risk of interruption of the inductor current, which usually causes damage to the transistors. In the paper principles of the system operation are described in detail and rules of component selection are presented. Laboratory tests were performed for different operating conditions. The test results have confirmed the operation correctness of the three-phase voltage source inverter with the proposed soft switching system.

Keywords: soft switching, switching losses, voltage source inverter

#### Streszczenie

Łagodne przełączanie tranzystorów w falownikach napięcia wymaga najczęściej stosowania dodatkowych elementów, takich jak tranzystory, kondensatory i dławiki indukcyjne. W odróżnieniu od istniejących rozwiązań, w proponowanym układzie łagodnego przełączania nie występuje niebezpieczeństwo udarowego rozładowania kondensatora przez tranzystor główny falownika oraz nie ma ryzyka przerwania prądu dławika, co grozi uszkodzeniem tranzystorów. Przedstawiono zasady pracy układu, wytyczne doboru elementów. Badania laboratoryjne przeprowadzono dla różnych warunków pracy. Wyniki badań potwierdziły poprawność działania trójfazowego falownika z proponowanym układem łagodnego przełączania tranzystorów.

Słowa kluczowe: falownik napięcia, łagodne przełączanie, straty przełączania

<sup>\*</sup> D.Sc. Ph.D. Witold Mazgaj, M.Sc. Bartosz Rozegnał, Ph.D. Zbigniew Szular, Institute of Electromechanical Energy Conversion, Faculty of Electrical and Computer Engineering, Cracow University of Technology.

#### 1. Introduction

Power losses generated in insulate gate bipolar transistors (IGBT), which are usually applied in voltage source inverters (VSI), are the sum of the conduction losses and the switching losses [1–4]. Users of these inverters do not have influence on the first type of the power losses, because these losses depend on the transistor current value and its voltage between the collector and the emitter during the conduction state. This voltage is mainly in the range of 1.5 V to 2.5 V. Reduction of the conduction losses is possible only by technological procedures during the manufacture of transistors.

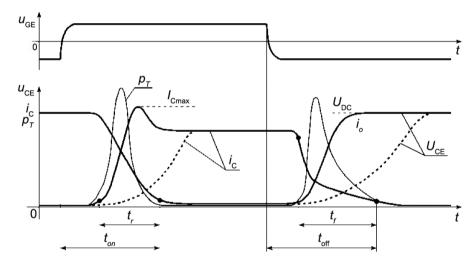

The switching losses occur during both the transistor turn-on and turn-off processes and they are caused by simultaneous changes of the transistor current and its voltage during the switching processes. These losses depend on the voltage supplying the given three-phase VSI, the load current, and the dynamic parameters of the applied IGBTs [5, 6]. The value of the switching losses depends significantly also on durations of changes of the transistor current and its voltage during the turn-on and turn-off processes. Fig. 1 presents simplified waveforms of the transistor current and voltage during the switching processes.

Fig. 1. Simplified waveforms during the switching processes:  $i_{\rm C}$  – transistor current,  $u_{\rm CE}$  – collector-emitter voltage,  $u_{\rm GE}$  – gate-emitter voltage, dashed lines – changes of the transistor current and voltage during the soft switching process

The turn-on losses  $P_{son}$  per one switching period are usually estimated with the use of the following formula:

$$P_{son} = \frac{1}{T_p} \int_{0}^{t_r} i_{Cr}(t) u_{CEr}(t) dt$$

(1)

where:

$T_p$  - switching period,

$u_{\text{CFr}}^{p}(t)$  – collector-emitter voltage during the turn-on process,

$i_{Cr}(t)$  – collector current during the turn-on process,

- current rise time in the turn-on process.

In turn, the losses  $P_{soff}$  occurring during the turn-off process can be estimated similarly:

$$P_{soff} = \frac{1}{T_p} \int_0^{t_f} i_{Cf}(t) u_{CEf}(t) dt$$

(2)

where:

$u_{CEF}(t)$  – collector-emitter voltage during the turn-off process,

$i_{C}(t)$  – collector current during the turn-off process,

$t_f$  – current fall time in the turn-off process.

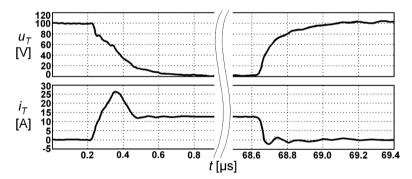

Figure 2 shows an example of the current and the voltage waveforms of the IGBT type IRG4PH50KD (1200 V, 24 A) during the hard switching process in the three-phase laboratory voltage source inverter. The transistor current after the turn-on process was equal to 12 A, and the voltage at the end of the turn-off process reached a value of 100 V;  $t_r$  and  $t_f$  times of this transistor are respectively 72 ns and 390 ns. The transistor switching losses in a single cycle at the frequency of 3 kHz were approximately equal about 1.17 W for the mentioned current and voltage values.

Fig. 2. Waveforms of the transistor current and voltage during both the turn-on and turn-off processes in the three-phase voltage source inverter

The share of the switching losses in the total power losses occurring in the IGBTs rises with the switching frequency. This problem particularly concerns the VSIs, which operate with the pulse width modulation (PWM). In many cases, these losses are greater than the conduction losses at the switching frequency of a few kHz. An increase of these losses leads not only to a reduction of the inverter efficiency, but it can cause problems with proper cooling of IGBTs. It is worth underlining that the estimation of the total switching losses in VSIs needs to take into account the losses occurring in freewheeling diodes of transistors.

The pursuit of a reduction of the switching losses is to increase the efficiency of power electronic inverters; on the other hand, less switching losses lead to an improvement of cooling systems of IGBTs. The fulfilment of the second requirement is often more important than an improvement of the efficiency, especially in medium and high power inverters.

# 2. Soft switching systems in three-phase voltage source inverters

The switching losses can be significantly reduced by using different methods of the soft switching of IGBTs. During the soft switching process, the transistor current or the collector-emitter voltage should be close to zero. In the first case, the switching process is called the zero current switching (ZCS); in the second case, the zero voltage switching (ZVS). Simplified waveforms of the transistor current and voltage during the soft switching process are shown in Fig. 1 by dashed lines.

Soft switching systems, which are used in the three-phase two-level voltage source inverters, can be divided into two groups. The first one includes cases in which VSIs have only one soft-switching systems for all transistors [7–13]. The main disadvantage of these systems is the possibility of soft switching in a relatively narrow range of the switching frequency. Such soft switching systems are applied, for example, in PWM rectifiers, which are connected to an AC grid, and they operate at the constant frequency of 50 Hz or 60 Hz [14, 15]. The second group includes systems that support the switching processes of IGBTs individually in each phase of the given VSI. These systems are used in inverters which operate at a relatively high switching frequency, in particular in inverters operating with the PWM.

The most frequently used systems of individual soft switching in each phase consist of two additional auxiliary transistors, one or more inductors and two capacitors, which are usually parallel connected to the main transistors in all phases of the given VSI [16–22]. In some soft switching devices, the auxiliary transistors are connected to the main transistors by means of special transformers [21, 23–25].

The primary disadvantage of hitherto applied soft switching systems in VSIs is a risk of situation when one of the main transistors is turning-on and the parallel connected capacitor is not unloaded. Additionally, in existing soft switching systems, another danger occurs when any auxiliary transistor is turning-off at a non-zero current of the inductor, which is connected in series to the given auxiliary transistor. This may be caused by signal disturbances in control system. In the first case, the main transistor can be damaged due to the flowing of an impulse current. In the second case, an overvoltage can occur on the inductor connected in series to the given auxiliary transistor, and it can lead to damage of this transistor. It should be noticed, that in some soft switching systems, the parasitic output capacitance of the transistor is used, mainly of MOSFETs, but this proposal concerns the soft switching systems with a relatively lower nominal power. In medium and high power VSIs, it is not possible due to the small value of the input transistor capacitance, which is usually close to 1–2 nF.

A certain drawback of the existing soft switching systems is also the quite complicated control system of both the main and auxiliary transistors. In the most cases, before the turn-on process of the main transistors, the appropriate auxiliary transistors have to be turned-on at a very precisely selected time. This leads to a significant complication of the switching algorithm, especially in inverters operating with the PWM.

# 3. Proposal of novel soft switching system

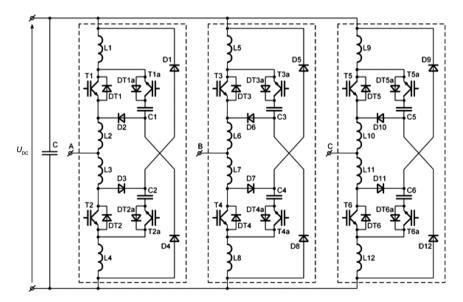

Drawbacks of the existing soft switching methods in VSIs, mentioned in the previous chapter, do not occur in the proposed soft switching system presented in Fig. 3, which shows connections of the elements in one phase of the three-phase two-level VSI [26]. Each main transistor of the given VSI has an individual soft switching system, which consists of one auxiliary transistor, one capacitor and two inductors. It is necessary to stress that in some soft switching methods, both the main and auxiliary transistors should be turned-on and turned-off at their current or voltage, which are close to zero.

The collector of the main transistor T1 is connected through the inductor L1 to the positive terminal of the DC supply source, which consists of a real voltage source and parallel connected capacitor C. The emitter of this transistor is connected through the inductor L2 to the output terminal of the VSI (phase A). The collector of the bottom transistor T2 is connected to this output terminal through the inductor L3, which has the same inductance as the inductor L2. The capacitors C1, C2 are connected in series to the respective auxiliary transistors T1a, T2a.

Fig. 3. Three-phase voltage source inverter with the novel soft switching system

In the proposed soft switching system, the capacitors are not directly connected in parallel to the main transistors and the inductors are not series connected to the auxiliary transistors. These are significant advantages in relation to existing soft switching methods in three-phase two-level VSIs. In the proposed system a sudden interruption of the inductor current or an impulse discharging of the capacitors cannot occur; it has significant meaning during disruptions, which may appear in the control system of the VSI. The capacitors C1, C2 reduce the rate of the voltage increase of the main transistors during the turn-off

processes. In turn, the inductors L1, L4 influence the rate of the current increase of the main transistor during the turn-on processes.

The auxiliary transistors are turned-on with a small delay with respect to the turn-on moments of the main transistors. This delay depends on the time when the main transistor current reaches the value of the load current. In turn, the auxiliary transistors are turned-off after the end of the resonant capacitor discharge processes, but not later than turn-off processes of the corresponding main transistors. Thus, the auxiliary transistors can be turned-off at the same times as the main transistors.

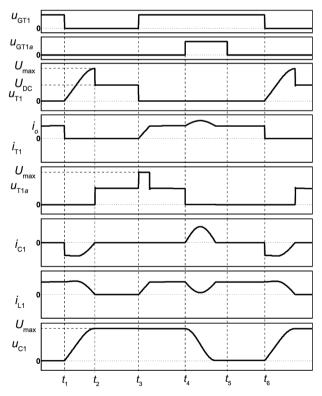

In order to simplify the description of the operation of the proposed soft switching system, it was assumed that the load phase current does not change its value during one period of the transistor switching. In the initial state of analysis, the transistor T1 is in the conducted state, other transistors do not conduct, the capacitor C1 is discharged, but the voltage of the capacitor C2 is equal to the DC supply source voltage. At the initial moment, the current flows from the positive terminal of the DC supply source trough the inductor L1, transistor T1, inductor L2 to the phase A of the load. Simplified waveforms of chosen currents and voltages of one inverter phase are shown in Fig. 4.

Fig. 4. Simplified waveforms in the proposed soft switching system:  $u_{\rm GTI}$ ,  $u_{\rm GTIa}$  – control signals of the main transistor T1, and auxiliary transistor T1a,  $u_{\rm T1}$ ,  $i_{\rm T1}$  – voltage and current of the transistor T1,  $u_{\rm T1a}$  – voltage of the auxiliary transistor T1a,  $i_{\rm C1}$ ,  $u_{\rm C1}$  – current and voltage of the capacitor C1,  $i_{\rm L1}$  – current of the inductor L1

At time  $t_i$ , the transistor T1 is turning-off, and its current decreases rapidly to zero. The capacitor C1 charges resonantly to a voltage, which is higher than the DC supply voltage  $U_{\rm DC}$ , and the capacitor current flows through L1, DT1a, C1, D2, L2, phase A of the load. The current flowing through the inductor L1 and capacitor C1 decreases to zero; at the same time the capacitor voltage and the voltage of the main transistor T1 increases and reaches a certain maximum value at time  $t_3$ . The current of the phase A flows from the negative terminal of the DC supply source partially through D4, D2, L2, and partially through L4, DT2, L3. Values of these currents depend on the inductor inductances, their resistances, and on voltage drops occurring on diodes in the conduction states. The voltage of the main transistor T1 approaches the DC source voltage  $U_{\rm DC}$ . Due to the charging of the capacitor C1, the voltage of the transistor T1 is close to zero during the turn-off process; so, we can state that the turn-off process of this transistor has the soft character. In the time interval  $t_2$ ,  $t_3$  transistor T1 still does not conduct and voltages on individual elements do not change their values. At time  $t_3$  the main transistor T1 is turning-on; the current flowing through the inductor L1 and transistor T1 slowly increases to the value of the load current. At the same time the currents, which flow partially through diodes D2, D4 and partially through L4, D3, L3, begin to decrease to zero. Due to the slow increase of the current of the inductor L1, the turn-on process of the transistor T1 has the soft character. The auxiliary transistor T1a is turning-on at time  $t_a$ , and then the capacitor C1 begins to discharge resonantly in the circuit, which consists of following elements: C1, T1a, L1, DC supply source, D4. The current of the inductor L1 decreases; this causes a certain reduction of the power consumed from the DC supply source. The auxiliary transistor T1a is turned-off at time  $t_5$  when the resonant discharge of the capacitor C1 is ended, but no later than the turn-off of the main transistor T1. At time  $t_6$  the transistor T1 is turned-on again and the next cycle of the system operation begins.

Due to the resonant character of the capacitor current, the auxiliary transistor Tla is turned-on and turned-off at the current value, which is close to zero, so the switching processes of this transistor also have a soft character. For properly selected values of the capacitance and inductances, the capacitors should be discharged to the voltage close to zero. Since time  $t_5$  the auxiliary transistor Tla is in the non-conduct state; in turn, the main transistor Tl still conducts, and the current flows from the positive terminal of the DC source through Ll, Tl, L2 to the phase A of the load. The capacitor Cl is in the discharged state to the moment when the main transistor Tl is turned-off again.

For the opposite direction of the load current, the second main transistor T2 and the second auxiliary transistor T2a of the given phase are switched similarly as the transistors T1, T1a.

#### 4. Selection of inductors and capacitors

The inductors, which connect the main transistors to the positive or negative terminal of the DC source, should limit the rate of the current increase so that the current value would be close to zero. When the switching frequency is higher than 1 kHz, the current of the given main transistor usually increases linearly with respect to time after the transistor turnon. When we assume that this current cannot be higher than the product of its maximum

value  $I_{T_{\text{max}}}$  (the maximum value of the load current) and a certain coefficient  $m_r$ , which can range from zero to one, the inductance of the inductors L1, L4 can be determined using the following formula:

$$L_{1.4} = \frac{U_{\rm DC}}{m_r I_{T_{\rm max}}} t_r \tag{3}$$

where:

t<sub>r</sub> - time of the current increase from 10% to 90% of its maximum value, determined on the basis of datasheets,

$m_{r}$  - ratio of the transistor current at time  $t_{r}$  to the  $I_{T \text{max}}$  value.

The parameter  $t_r$  depends on the operation conditions and also the resistance of the gate-emitter circuit has significant influence on time  $t_r$ . In order to reduce the switching losses in the turn-on processes, the value of the coefficient  $m_r$  should decrease; however, then the inductors L1, L4 should have higher inductances. It is worth underlining that the power losses in the turn-off process can be divided into the ones generated during the current decreasing and the losses occurring during stabilizing of the transistor off-state [27].

The turn-off process of the main transistor has the soft character if the appropriate capacitor is fully discharged before the start of this process. This condition is fulfilled when the maximum value of the capacitor voltage  $U_{\rm max}$  is at least twice the voltage of the DC supply source  $U_{\rm DC}$ . On the other hand, the voltage  $U_{\rm max}$  cannot be arbitrary high due to the transistor nominal voltage. After the turn-off process of the main transistor T1 (Fig. 3), the current of the inductor L1 flows through the freewheeling diode of the auxiliary transistor T1a; so the magnetic field energy stored in the inductor L1 is converted into energy of the electric field of the capacitor C1. Thus, the capacitance of the capacitors C1, C2 can be determined on the basis of the following formula:

$$C_{1.2} = L_{1.4} \frac{I_{T_{\text{max}}}^2}{\left(k_{\text{C}}U_{\text{DC}}\right)^2} \tag{4}$$

where:

$k_{\rm C}-$  ratio of the maximum value of the capacitor voltage with respect to the voltage  $U_{\rm DC}$  of the supply source.

The value of the coefficient  $k_{\rm C}$  depends on the supply voltage of the given VSI and on the maximum value of the load current. For currents 400–500 A, the IGBTs with nominal voltages up to 3.3 kV are available as standard products. It is necessary to underline that all IGBTs should be selected with respect to the maximum voltage that can occur on the capacitors; it is a certain shortcoming of the proposed soft switching system.

The inductors L1, L4 and the capacitors C1, C2 influence the resonant discharge time of the capacitors and they have significant influence on the rate of the discharge current, which flows through the auxiliary transistors. The turn-on losses of these transistors depend on the value of the discharge current when the auxiliary transistors are turned-on. This current can be determined with the use of the formula:

$$i_{T1a}(t_r) = (U_{\text{Cmax}} - U_{\text{DC}}) \sqrt{\frac{C_{1.2}}{L_{1.4}}} \sin \frac{t_r}{\sqrt{L_{1.4} C_{1.2}}}$$

(5)

The inductors L2, L3 protect the capacitor against impulse discharge through the DC supply source. Determination of their inductance is not critical; laboratory research indicates that the inductance of these inductors can have the same value as the inductance of the inductor connecting the main transistors to the positive or negative terminal of the DC supply source.

# 5. Laboratory research

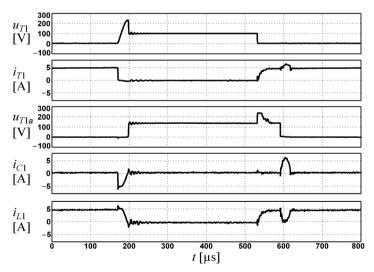

Verification of the correctness of the proposed soft switching system was carried out using the voltage source inverter with the power of about 3 kW, which was built on the basis of the IGBTs type G4PH50KD. The inverter was supplied from the DC source 100 V; the maximum load current was equal to 14 A. Figure 5 presents waveforms of chosen currents and voltages for the following parameters: C1, C2 = 1  $\mu$ F, L1, L2, L3, L4 = 300  $\mu$ H, switching frequency  $f_i$  = 1 kHz, coefficient of amplitude modulation  $m_a$  = 0.8. The maximum voltage of the capacitors did not exceed 250 V. The current of the transistor T1 in the turn-on process reached a value of about 0.6 A at the load current of 4.25 A, and the voltage of this transistor during the turn-off process was equal to 14 V ( $U_{DC}$  = 100 V). It is worth underlining that the current of the auxiliary transistor T1a reached the value 1 A after it is turned-on. The turn-off process of this transistor occurs at zero voltage due to the conduction state of the main transistor T1. The switching losses of the main and auxiliary transistor were about 0.04 W and 0.035 W (at PWM frequency 1 kHz), respectively. The total switching losses of both transistors in the proposed system accounted for about 11% (0.52 W) of the losses of one main transistor during "hard" switching process in the inverter without soft switching system.

Fig. 5. Waveforms of chosen voltages and currents in the laboratory voltage source inverter with the proposed soft switching system:  $i_{DC} = 4,25 \text{ A}, f_i = 1 \text{ kHz}, m_a = 0,8, C1, C2 = 1 \mu\text{F},$  L1, L2, L3, L4 =-300  $\mu$ H; description of waveforms as in Fig. 4

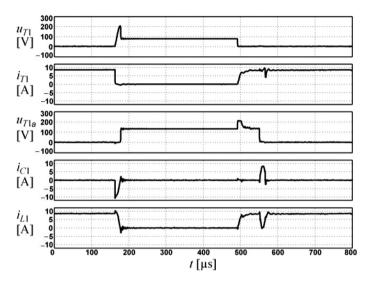

Figure 6 shows analogous waveforms in the case when the inductance of the inductors L1, L4 was equal to  $120~\mu H$  and the inverter transistors were switched at the frequency of 1 kHz. The decrease of this inductance causes faster increase of the main transistor current after its turn-on, but then the switching losses of both transistors are quite higher, and they are about 0.12~W.

Fig. 6. Waveforms of chosen voltages and currents in the laboratory voltage source inverter with the proposed soft switching system;  $i_{DC}$  = 7 A,  $f_i$  = 1 kHz, C1, C2 = 1 mF, L1, L4 = 120  $\mu$ H, L2, L3 = 300  $\mu$ H; description of waveforms as in Fig. 4

It should be noted that the decrease of the inductor inductance L1, L4 leads to a reduction of the capacitor maximum voltage. However, for the correct operation of the soft switching system, this voltage should be about twice the voltage of the DC supply source.

#### 6. Conclusions

In the proposed soft switching system, the capacitors cannot discharge rapidly through the main transistor and it is impossible to interrupt the current of the inductors, e.g. due to control distortions. When control signals of the auxiliary transistors are not synchronized with the switching signal of the main transistors, a "hard switching" of transistors occurs, rather than device failure.

The control method of the transistor switching is simple because the auxiliary transistors are turned-on with a small delay with respect to the turn-on moments of the main transistors. Additionally, the auxiliary transistors are turned-off after the end of the resonant capacitor discharge processes. Thus, the auxiliary transistors can be turned-off at the same times as the main transistors.

The proposed soft switching system protects transistors against overvoltages due to the occurrence of the capacitors. The use of the inductors is also important in the event of unintentional switching to conduction of both the main transistors in the given phase. Slower increase of the transistor current gives more time to operate of the circuit protection, which is important, especially in medium and high power inverters.

Reduction of switching losses increases the efficiency of the voltage source inverter and also simplifies a transistor cooling system, which can be crucial for medium and high power inverters.

### Acknowledgements

The research presented in this paper was funded by subsidies on science granded by Polish Ministry of Science and Higher Education under the theme No. E-2/616/2016/DS "Reduction of losses in three-phase, two-level voltage source intervers by applying the soft switching system which is resistant to control disturbances".

#### References

- [1] Feix G., Dieckerhoff S., Allmeling J., Schonberger J., Simple Methods to Calculate IGBT and Diode Conduction and Switching Losses, 13th European Conference on Power Electronics and Applications, EPE '09, Barcelona, Spain, 8–10 September 2009, 1–8

- [2] Drofenik U., Kolar J.W., A General Scheme for Calculating Switching and Conduction-Losses of Power Semiconductors in Numerical Circuit Simulations of Power Electronic Systems, 5th International Power Electronics Conference, IPEC-Niigata, Japan, 2005.

- [3] Maswood A.I., *A switching loss study in SPWM ight inverter*, 2nd IEEE International Conference on Power and Energy, PECon 08, Johor Baharu, Malaysia, 1–3 December 2008, 609–613.

- [4] Rajapakse A.D., Gole A.M., Wilson P.L., *Approximate Loss Formulae for Estimation of IGBT Switching Losses through EMTP-type Simulations*, International Conference on Power Systems Transients, IPST'05, Montreal, Canada, 19–23 June 2005, Paper No. 184, 1–6.

- [5] Hiraki E., Tanaka T., Nakaoka M., *Zero-Voltage and Zero-Current Soft -Switching PWM Inverter*, 36th Power Electronics Specialists Conference PESC '05, Recife, Brazil, 12–16 June 2005, 798–803.

- [6] Martinez B., Li R., Ma K., Xu D., *Hard Switching and Soft Switching Inverters Efficiency Evaluation*, International Conference on Electrical Machines and Systems ICEMS 2008, Wuhan, China, 17–20 October 2008, 1752–1757.

- [7] Amini M.R., Farzanehfard H., *Three-Phase Soft-Switching Inverter With Minimum Components*, IEEE Transactions on Industrial Electronics, vol. 58, June 2011, Iss. 6, 2258–2264.

- [8] Khalilian M., Farzanehfard H., Adib E., A novel quasi-resonant three-phase softswitching inverter, 3rd Power Electronics and Drive Systems Technology, PEDSTC, 2012, 471–476.

- [9] Liu Y., Wu W., Blaabjerg F., Chung H.S., A modified two-level three-phase quasi-softswitching inverter, Twenty-Ninth Annual IEEE Applied Power Electronics Conference and Exposition, APEC, 2014, 261–267.

- [10] Panda B., Bagarty D.P., Behera S., *Soft-switching dc-ac Converters: A brief literature review*, International Journal of Engineering Science and Technology, vol. 2, 2010, 7004–7020.

- [11] Shukla J., Fernandes B.G., *Three-phase soft-switched PWM inverter for motor drive application*, Electric Power Applications, IET, vol. 1, Jan. 2007, 93–104.

- [12] Wang K., Jiang Y., Dubovsky S., Hua G., Boroyevich D., Lee F.C., Novel DC-Rail Soft-Switched Three-Phase Voltage-Source Inverters, IEEE Transactions on Industry Applications, vol. 33, 1997, 509–517.

- [13] Wu W., Geng P., Chen J., Ye Y., *A Novel Three-Phase Quasi-Soft-Switching DC/AC Inverter*, IEEE International Symposium on Power Electronics for Distributed Generation Systems, PEDG, Hefei, China, 16–18 June 2010, 477–480.

- [14] Vlatkovic V., Borojevic D., Lee F.C., Zero-voltage switched three-phase PWM rectifier inverter circuit, Patent US5432695, US 1995.

- [15] Xu D., Feng B., *Novel ZVS Three-Phase PFC Converters and Zero-Voltage-Switching Space Vector Modulation (ZVS-SVM) Control*, IEEE First International Conference on Power Electronics Systems and Applications, Hong Kong, China 2004, 30–37.

- [16] Chandhaket S., Yoshida M., Eiji H., Nakamura M., Konishi Y., Nakaoka M., Multi-functional Digitally-Controlled Bidirectional Interactive Three-phase Soft-Switching PWM Converter with Resonant Snubbers, IEEE 32nd Annual Power Electronics Specialists Conference, PESC, vol. 2, Vancouver, Canada 2001, 589–593.

- [17] Chao K.H., Liaw C.M., *Three-phase soft-switching inverter for induction motor drives lyomori-Three*, IEE Proceedings Electric Power Applications, vol. 148, Jan 2001, 8–20.

- [18] Galea C., *New topology of three phase soft switching inverter using a dual auxiliary circuit*, 15th European Conference on Power Electronics and Applications, EPE 2013, 1–9.

- [19] Karyś S., Power loss comparison for the ARCP resonant inverter regard to control method, Przegląd Elektrotechniczny, 84, nr 11, 2008, 64–68.

- [20] Li Y., Lee F.C., Boroyevich D., A Three-Phase Soft-Transition Inverter with a Novel Control Strategy for Zero-Current and Near Zero-Voltage Switching, IEEE Transactions on Power Electronics, vol. 16, Sep 2001, 710–723.

- [21] Martinez B., Li R., Ma K., Xu D., *Hard Switching and Soft Switching Inverters Efficiency Evaluation*, International Conference on Electrical Machines and Systems, ICEMS, Wuhan, China, 17–20 October 2008, 1752–1757.

- [22] Keir A.S., Soft switched three-phase inwerter with staggered resonant revovery system, Patent US5576943, US 1996.

- [23] Karyś S., *Three-Phase Soft-Switching Inverter with Coupled Inductors, Experimental Results*, Bulletin of the Polish Academy of Sciences Technical Sciences, 59, Warsaw, Zeszyt 4, Grudzień 2011, 535–540.

- [24] Zhang H., Chu E., Liu X., Wang Q., Hou L., Resonance electrode type three phase soft switch inverter circuit, Patent CN101478258 (A), China 2010.

- [25] Sun P., Lai J., Qian H., Yu W., Smith C., Bates J., *High Efficiency Three-Phase Soft-Switching Inverter for Electric Vehicle Drives*, IEEE Vehicle Power and Propulsion Conference, VPPC '09, Dearborn, USA, 7–10 Sept. 2009, 761–766.

- [26] Mazgaj W., Rozegnał B., Szular Z., Sposób łagodnego przełączania tranzystorów trójfazowego, dwupoziomowego falownika napięcia oraz układ łagodnego przełączania tranzystorów trójfazowego, dwupoziomowego falownika napięcia (in English The method and system of soft switching of transistors in the three-phase, two-level voltage source inverter), Patent Application P.412114, 2015.

- [27] Špánik P., Dobrucký B., Frívaldský M., Drgoňa P., Kurytnik I., *Measurement of switching losses in power transistor structure*, *E*lectronics and Electrical Engineering/ Elektronika ir Elektrotechnika, No. 2 (82), 2008, 75–78.